/https://www.ilsoftware.it/app/uploads/2023/05/img_14482.jpg)

In attesa dell'”arrivo” di transistor non lineari, sui quali stanno lavorando gli accademici dell’Università della Carolina del Nord (Nuovo design per i transistor farà dimenticare la legge di Moore?), i ricercatori dell’Università di Berkley hanno proposto alcune innovazioni che, nel frattempo, potrebbero consentire di miniaturizzare ulteriormente i dispositivi a semiconduttore, rendendo fattibile un processo costruttivo a 1 nm.

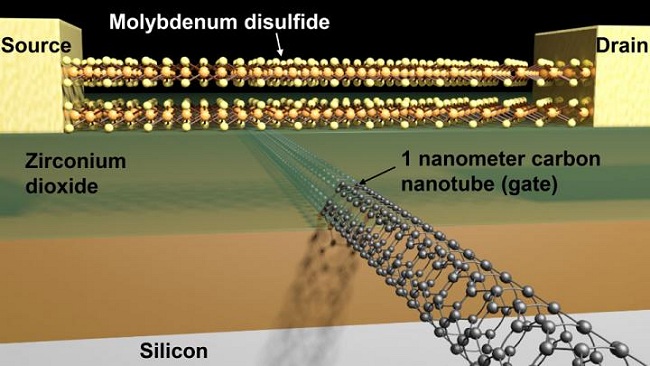

L’esemplare di transistor, funzionante, realizzato a Berkley mette da parte il silicio come materiale principale ed è stato messo a punto ricorrendo ai nanotubi di carbonio e al disolfuro di molibdeno (formula chimica MoS2).

Il processo costruttivo da 1 nm consentirebbe di inserire ben 80.000 transistor nello stesso spazio occupato, ad esempio, da un capello umano.

Basti pensare che Intel realizza i suoi processori più moderni ricorrendo a un processo costruttivo a 14 nm e i 10 nm rappresentano il prossimo balzo tecnologico (vedere Intel presenterà i suoi processori a 7 nm nel 2020).

Altre aziende, come Samsung, stanno già producendo SoC a 10 nm destinati ai dispositivi mobili.

Gli autori dello studio, comunque, consigliano di usare cautela: i transistor da 1 nm non sono stati ancora “impacchettati” in un chip e non vi sono ancora conferme in termini di affidabilità (l’operazione, insomma, non è stata ancora ripetuta più e più volte).

Certo è che MoS2 e nanotubi di carbonio aiutano a risolvere le problematiche ben note quando si ha a che fare con il silicio. Al di sotto dei 5 nm, il movimento degli elettroni diventa talvolta incontrollabile tanto che il transistor spesso, continuerà, ad assorbire corrente. Inoltre, il comportamento degli elettroni non è più regolato dai meccanismi della fisica classica ma si entra nel campo della meccanica quantistica.

Già di per sé MoS2 offre una buona soluzione perché gli elettroni si muovono come se fossero più pesanti che nel silicio (più lentamente). E se sulla carta i chip basati su questi transistor possono essere meno performanti, essi aiutano a spingere la miniaturizzazione all’estremo.

Inoltre MoS2 forma naturalmente fogli dello spessore di un singolo atomo rendendo così fattibile la realizzazione di dispositivi ipercompatti.

Per la realizzazione del gate e, quindi, del componente che controlla quando il transistor conduce e quando ciò non avviene, si è ricorsi ai nanotubi di carbonio che hanno permesso di realizzare la struttura nelle dimensioni più appropriate.

L’espressione processo costruttivo, nel caso di CPU e SoC, lo ricordiamo, ha a che fare con le dimensioni dei transistor. In particolare, il valore espresso in nanometri (nm) indica la dimensione media del gate di ciascun transistor usato nel processore.

/https://www.ilsoftware.it/app/uploads/2024/04/chip-amd-ryzen-ai-pro-8000.jpg)

/https://www.ilsoftware.it/app/uploads/2024/04/google-axion-cpu-ARM.jpg)

/https://www.ilsoftware.it/app/uploads/2024/04/acceleratore-intel-gaudi-IA.jpg)

/https://www.ilsoftware.it/app/uploads/2024/04/microcodice-AMD-architettura-AM5-plus.jpg)