/https://www.ilsoftware.it/app/uploads/2023/05/img_23124.jpg)

Sebbene l’industria stia guardando sempre più a materiali innovativi, il silicio rimane il componente fondamentale per l’intera industria dell’elettronica. È il secondo elemento più diffuso sulla Terra dopo l’ossigeno e si trova anche nella sabbia comune, quella che si trova in spiaggia.

Il silicio policristallino pesantemente drogato (si chiama drogaggio il processo che modifica le proprietà di un elemento attraverso l’aggiunta di impurità chiamate droganti) è un ottimo semiconduttore. Il drogaggio permette di aumentare infatti la sua conduttività di un fattore pari a oltre un miliardo. All’occorrenza, quindi, il silicio policristallino può condurre o isolare in modo ottimale.

In un altro articolo abbiamo visto come funziona un processore. Questa volta ci concentriamo sui processi che vengono applicati all’interno delle fonderie.

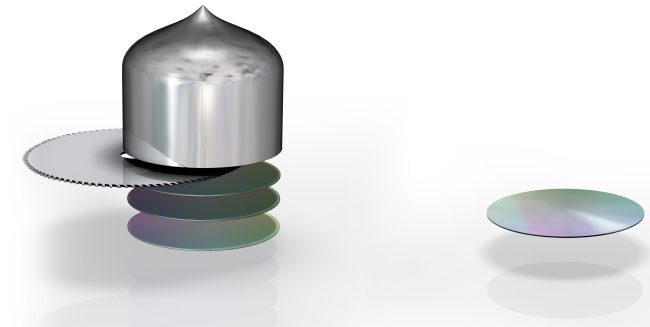

Per l’utilizzo in elettronica il silicio viene purificato in modo tale da avere un solo atomo impuro ogni due miliardi. Ricorrendo alla tecnica Czochralski il silicio viene fuso ed estratto a formare un lingotto solido di forma cilindrica (generalmente di diametro pari a 30 centimetri e peso pari a 100 chilogrammi) che viene “affettato” a formare il wafer con uno spesso di 1 millimetro (ecco perché i wafer di silicio sono sempre rotondi).

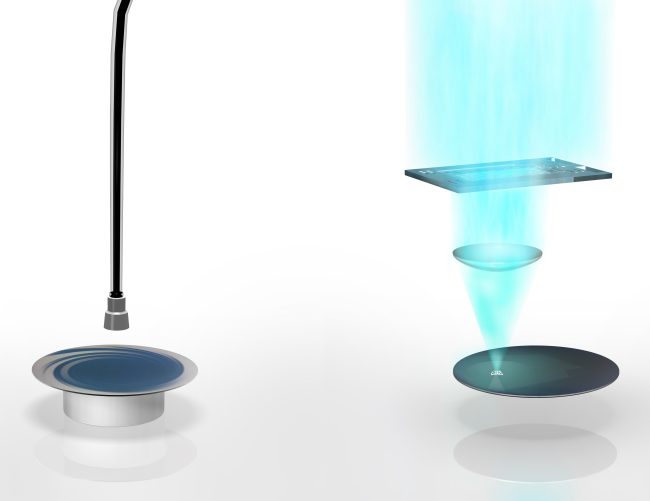

Il passaggio successivo che porta alla realizzazione di un processore consiste nell’utilizzo della tecnica della fotolitografia: essa permette di stampare sul wafer in silicio uno schema che permetterà poi di disporre i transistor e realizzare i vari chip.

Sul wafer fatto ruotare su se stesso viene applicato un liquido fotoresistente in modo da assicurarne l’applicazione uniforme su tutta la superficie. Si tratta di un materiale che è sensibile alla luce ultravioletta su specifiche frequenze mentre resiste ad alcune sostanze chimiche usate per eliminare successivamente le parti di materiale che si desiderano rimuovere dalla superficie del wafer.

Usando delle maschere, una volta che il liquido fotoresistente si è solidificato, il materiale fotoresistente viene esposto alla luce ultravioletta in modo tale da illuminare lo schema che deve essere trasferito sul wafer. Il processo è ripetuto per migliaia di volte, fino a circa 70.000 nel caso di in singolo wafer da 30 centimetri di diametro), per tante volte cioè quanti sono i chip che si possono ottenere.

L’area del wafer è pari infatti a 225 cm2 (Pi * r2). Supponendo di realizzare chip appena da 1 mm2 destinati a svolgere funzioni relativamente semplici si possono ottenere fino a 70.000 chip.

Viceversa, supponendo di produrre chip molto più grandi e complessi con un’area del die di 200 mm2 con lo stesso wafer da 30 centimetri di diametro se ne realizzerebbero appena 148.

Ovviamente alcuni chip risulteranno alla fine inutilizzabili a causa di difetti di produzione random abbassando la “resa”. Anzi, realizzando chip contraddistinti da un die di grandi dimensioni si rischia di aumentare la difettosità: per semplificare, supponendo di avere 50 difetti nel singolo wafer, nel caso dei chip da 1 mm2 si avrà una percentuale dello 0,07% in termini di difetti; dello 0,34% nel caso dei chip più grandi da 200 mm2.

Ciò porta a una resa rispettivamente del 99,93% e del 34%: una bella differenza!

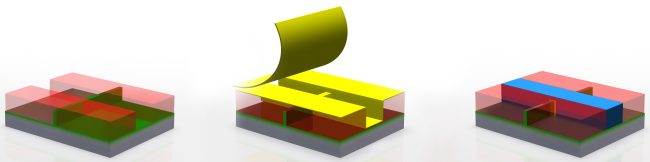

Il processo che porta alla realizzazione del processo prosegue con la fase ion implantation: si tratta della fase di drogaggio alla quale abbiamo fatto riferimento in apertura. Essa consiste nel bombardare il wafer di silicio con atomi a carica positiva o negativa per rendere il materiale conduttivo o isolante nelle aree precedentemente identificate attraverso l’uso della maschera.

Quando il materiale resistente viene rimosso si avrà l’area pronta per la realizzazione e il posizionamento del transistor vero e proprio (nei moderni processori ne sono contenuti miliardi; ad esempio gli AMD EPYC di seconda generazione del 2019 utilizzano 40 miliardi di transistor).

Il valore espresso in termini di nanometri (nm) indica la dimensione media del terminale gate che compone ciascun transistor. In un altro articolo spieghiamo perché viene utilizzata questa unità di misura e qual è il suo ruolo nella descrizione di un processore.

Fare esclusivamente riferimento al numero dei nanometri per presentare un processo produttivo è diventata un po’ una leva di marketing. Fare paragoni basandosi solo sul numero di nanometri è intrinsecamente scorretto tanto che Intel sembra intenzionata a cambiare nomenclatura.

Unendo in sequenza processi di fotolitografia con processi chimici viene costruita la struttura del tipico transistor tri-gate quindi con sviluppo tridimensionale.

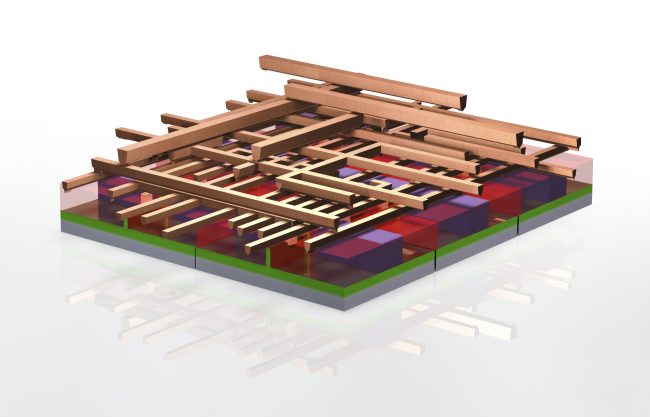

Al di sopra dei transistor, vengono disposti una serie di strati metallici. Anche se all’apparenza il circuito sembri avere una struttura planare, è possibile sovrapporre decine di strati che collegano i vari transistor in una fitta rete.

Da ultimo i chip vengono tagliati, impacchettati e verificati affinché non presentino problemi di funzionamento: i chip difettosi vengono scartati o comunque vengono segnalate le aree che presentano problemi.

Anche perché i chip con qualche problema di solito non vengono cestinati: un processore che avrebbe dovuto avere “n” core viene commercializzato con un numero di core inferiore se alcuni di essi non funzionano (vengono disattivati prima dell’immissione sul mercato); viene indicato senza GPU integrata se la sezione grafica presenta problemi.

Il chip viene unito con un substrato di colore verde (facilmente individuabile nei processori che acquistiamo) e con un diffusore posizionato nella parte superiore. Il primo ha il compito di offrire l’interfaccia per l’interazione con la scheda madre mentre il secondo di diffondere il calore generato durante il funzionamento del processore (poi rimosso mediante l’eventuale applicazione di un dissipatore attivo o passivo).

Le immagini pubblicate nell’articolo sono tratte da “From sand to circuits” a cura di Intel.

/https://www.ilsoftware.it/app/uploads/2026/04/chip-intel-serpent-lake-nvidia-rtx.jpg)

/https://www.ilsoftware.it/app/uploads/2026/04/collaborazione-intel-arm.jpg)

/https://www.ilsoftware.it/app/uploads/2026/03/intel-core-ultra-series-3-processori-business.jpg)

/https://www.ilsoftware.it/app/uploads/2026/03/chip-arm-agi-cpu.jpg)