L’architettura RISC-V è emersa come una delle innovazioni più dirompenti nel panorama dell’ingegneria dei processori. Nata nei laboratori dell’Università di Berkeley come progetto accademico nel 2010, oggi rappresenta un movimento globale che sta ridefinendo il modo in cui si progettano CPU, microcontrollori e sistemi embedded. La sua forza risiede nella libertà architetturale: RISC-V è un’ISA (Instruction Set Architecture) open source, aperta e modulare, che chiunque può implementare senza pagare licenze o royalties.

La sovranità tecnologica e il controllo della supply chain sono diventati temi centrali: RISC-V si propone come alternativa ai modelli proprietari di x86 e ARM. Governi, università e colossi industriali – da Google a NVIDIA, da Qualcomm a Huawei – stanno investendo nella sua adozione, attratti dalla possibilità di personalizzare le istruzioni, ottimizzare il consumo energetico e sviluppare soluzioni su misura per AI, automotive, IoT e HPC.

Cos’è RISC-V in breve

Come accennato in precedenza, RISC-V (si legge “risc five“) è un’ISA aperta e libera (royalty-free) basata sui principi RISC (Reduced Instruction Set Computer). L’ISA definisce il “contratto” tra software e hardware: insiemi di istruzioni, dimensione dei registri, modalità privilegiate, formati binari e convenzioni ABI.

RISC-V è progettata per essere modulare: esiste un nucleo minimale (base integer) e una serie di estensioni standard che si possono combinare (es.: M per multiplication/division, A per atomic, F/D per floating-point, C per compressed, Z… per estensioni più piccole, RVV per vector). La specifica è pubblica e mantenuta da RISC-V International.

Varianti principali e concetti architetturali utili

⮞ RV32I / RV64I / RV128I: versioni base a 32, 64 o 128 bit (XLEN = 32/64/128) che determinano la larghezza dei registri interi e lo spazio di indirizzamento utilizzabile.

⮞ Estensioni standard: le già citate M, A, F/D, C (compressed, 16-bit) e una famiglia “Z” per estensioni opzionali come bit-manipulation (Zba, Zbb, …) o altre funzionalità. RVV è l’estensione vettoriale standard per SIMD/data-parallel.

- M (Multiply/Divide). Aggiunge le istruzioni per moltiplicazione e divisione intera. Senza questa estensione, un core RISC-V base non può eseguire direttamente operazioni aritmetiche complesse: dovrebbe emularle via software. È essenziale per prestazioni migliori nei calcoli numerici e nei microcontrollori avanzati.

- A (Atomic). Introduce le operazioni atomiche di memoria, come load-reserved e store-conditional, indispensabili per gestire multithreading e sincronizzazione tra core in sistemi multiprocessore o in codice concorrente.

- F / D (Floating Point). Forniscono supporto per il calcolo in virgola mobile, rispettivamente per numeri a precisione singola (F, 32 bit) e precisione doppia (D, 64 bit). Sono fondamentali per applicazioni scientifiche, grafiche e AI che richiedono aritmetica a virgola mobile hardware.

- C (Compressed). Abilita un set di istruzioni compresse a 16 bit, riducendo la dimensione del codice in memoria e migliorando l’efficienza dell’uso della cache. È molto utile nei sistemi embedded e IoT, dove la memoria è limitata.

- Famiglia “Z”. Raccoglie estensioni opzionali minori, ognuna con uno scopo specifico. Ad esempio, Zba per operazioni rapide su bit e indirizzi (es. shift, rotazioni); Zbb per la gestione di operazioni logiche avanzate, come conteggio dei bit o inversioni. Queste micro-estensioni servono a ottimizzare codice critico (crittografia, compressione, DSP).

- RVV (RISC-V Vector Extension). È l’estensione vettoriale standard per il calcolo SIMD (Single Instruction, Multiple Data) e parallelo, cioè l’esecuzione di una singola istruzione su più dati in parallelo. È pensata per elaborazioni di grandi quantità di dati, intelligenza artificiale, multimedia e calcolo scientifico.

⮞ Privileged spec: i livelli (User / Supervisor / Machine) e le estensioni per virtualizzazione, gestione MMU, e così via sono definite in uno standard separato (privileged spec, appunto), che è essenziale per eseguire sistemi operativi completi.

RISC-V: semplicità architetturale e sfide future secondo Linus Torvalds

RISC-V è considerata un’architettura più snella rispetto ad ARM e x86 grazie al suo design RISC e alla filosofia open source. La sua ISA di base definisce un set ridotto di istruzioni uniformi e di lunghezza fissa, con registri a 32, 64 o 128 bit (RV32I, RV64I, RV128I) e può essere estesa solo con le funzionalità necessarie (già viste nel paragrafo precedente).

Questa modularità consente di costruire core leggeri e ottimizzati per sistemi embedded, IoT o applicazioni ad alto throughput di dati, evitando il “fardello” della compatibilità storica che caratterizza x86 e ARM, dove molte funzionalità sono integrate per continuità anche quando non servono davvero.

Nonostante questa semplicità, Linus Torvalds ha messo in guardia: quando RISC-V diventerà una piattaforma diffusa, rischia di affrontare problemi simili a quelli incontrati da architetture consolidate. L’aggiunta di estensioni proprietarie e varianti hardware può generare frammentazione, rendendo più complesso il supporto software, la gestione del kernel Linux e la compilazione per diverse distribuzioni. Proprio di recente, a inizio ottobre 2025, il “re pinguino” aveva tuonato contro l’integrazione di Big Endian per RISC-V lato kernel.

Torvalds sottolinea inoltre che chi lavora a livelli più alti dello stack ha una visione limitata dei dettagli hardware, rendendo difficile anticipare problemi reali.

Le sfide non riguardano solo la compatibilità: vulnerabilità hardware come Spectre dimostrano quanto sia difficile correggere problemi già presenti in generazioni precedenti dei processori. Anche un’architettura aperta come RISC-V non è immune a rischi di sicurezza o a errori nella catena di sviluppo software. La fiducia nella comunità, nei contributori e nei produttori diventa quindi cruciale per garantire un ecosistema stabile e sicuro.

Com’è nata RISC-V e com’è cresciuto l’ecosistema

RISC-V è nato nel 2010 presso il ParLab dell’Università della California, Berkeley, per volontà di Krste Asanović e di altri accademici come progetto di ricerca che potesse essere un’ISA aperta e usabile sia in ambito didattico che commerciale.

Il lavoro in ambito universitario ha poi portato alla fondazione di RISC-V International che mantiene le specifiche. L’intento originale era creare un “core” semplice, estendibile e adatto a ricerca e industria.

L’ecosistema software attorno a RISC-V ha compiuto un salto di qualità notevole. Gli strumenti fondamentali per lo sviluppo — come i compilatori GCC e LLVM, gli strumenti di assemblaggio e linking (binutils) e l’emulatore QEMU — includono ormai un supporto maturo e ufficiale per l’ISA RISC-V, permettendo di compilare, eseguire ed emulare applicazioni senza ricorrere a soluzioni sperimentali.

Anche il kernel Linux ha integrato il supporto nativo (upstream) per RISC-V dal 2017. Ciò significa che le patch per l’architettura sono parte integrante del codice principale mantenuto da Linus Torvalds e dalla community. Chiunque può quindi compilare un kernel standard per RISC-V senza dipendere da versioni modificate o non ufficiali.

Supporto di RISC-V nelle distribuzioni Linux

Parallelamente, le distribuzioni Linux hanno iniziato a offrire versioni dedicate o porting:

- Fedora e Debian mantengono build ufficiali per RISC-V (note come alt-arch, cioè architetture alternative).

- Ubuntu e Rocky Linux stanno progressivamente includendo immagini sperimentali per hardware compatibile.

- Altre distribuzioni (come Arch e Gentoo) offrono supporto comunitario.

Tuttavia, un ostacolo importante è stato — e in parte rimane — la mancanza di una piattaforma hardware di riferimento unificata. Ogni produttore di SoC o scheda RISC-V (come SiFive, StarFive, Milk-V, ecc.) tende a implementare combinazioni diverse di estensioni ISA, periferiche e firmware. Un kernel o una distribuzione compilata per una board potrebbe non funzionare su un’altra senza modifiche ai device tree, ai driver o al bootloader.

Solo recentemente RISC-V International, insieme ai produttori e agli sviluppatori di distribuzioni, ha iniziato a definire dei “RISC-V Profiles” standard (come RVA22, RVA23,…), che specificano l’insieme minimo di estensioni e funzionalità hardware richieste per garantire compatibilità software.

I profili approvati centralmente mirano a fornire quella base comune che finora è mancata, permettendo alle distribuzioni di creare immagini ufficiali capaci di funzionare su più dispositivi senza modifiche sostanziali.

Schede e SoC acquistabili oggi (esempi pratici)

Negli ultimi anni sono comparsi sul mercato numerosi single-board computer (SBC) e moduli RISC-V, adatti per sperimentazione o progetti embedded/desktop:

- StarFive / VisionFive 2 (e VisionFive 2 Lite). SBC basate su SoC StarFive (JH-series). La versione Lite è presentata come SBC economico (varianti RAM 2–8GB). Ottima per testare Linux su RISC-V.

- SiFive HiFive Unmatched / HiFive (linea SiFive). Board desktop/mini-ITX per sviluppo RISC-V basate su core SiFive FU/U-series; pensate per sviluppo software e prototipazione ad alto livello.

- BeagleV-Fire (PolarFire SoC). SBC con Microchip PolarFire MPFS SoC (RISC-V + FPGA fabric), molto utile per co-design hardware/software e bootstrapping Linux + acceleratori programmabili.

- Milk-V Jupiter, LicheePi (Sipeed LicheePi 3A) e altre schede basate su SPACEMIT/SiPeed/SpaceMIT. Esempi di board più recenti con SoC octa-core RISC-V, spesso dotati di RVV e capacità multimediali/AI (utili in ambito desktop e per le applicazioni multimediali).

La qualità dei driver upstream, il livello di integrazione (WiFi, GPU, video) e la compatibilità con le distro varia molto da prodotto a prodotto.

Imparare a usare assembly per programmare i SoC RISC-V con EasyRISC-V

Se l’idea di scrivere istruzioni che parlano direttamente con la CPU ti elettrizza, EasyRISC-V è un nuovo strumento che permette di dare uno sguardo al cuore di un chip RISC-V, per adesso senza neppure comprarlo.

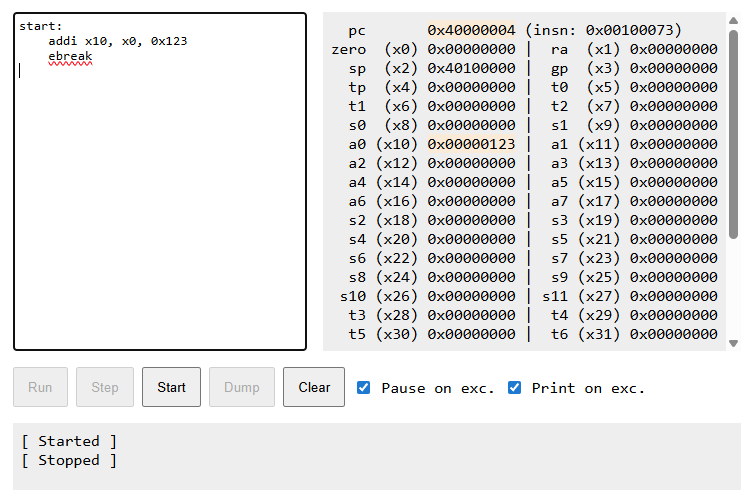

EasyRISC-V funziona interamente da browser Web e permette di provare, sbagliare e capire passo dopo passo come usare il linguaggio assembly per colloquiare con RISC-V.

Il sito è una guida interattiva incentrata sul sottoinsieme RV32I con le estensioni essenziali per i registri di controllo (Zicsr) e include un emulatore che permette di scrivere, assemblare ed eseguire codice senza installare nulla.

Imparare assembly non è (solo) tenere a mente delle regole mnemoniche: EasyRISC-V aiuta a pensare in termini di registri, indirizzi e regole di chiamata. Il fatto che l’emulatore mostri il codice in esadecimale e dove vengono mappati gli indirizzi rende manifesta la traduzione “istruzione → encoding” e aiuta a comprendere perché, ad esempio, esistono certe limitazioni.

Cosa troverai nel tutorial

Il contenuto del tutorial di EasyRISC-V è suddiviso in sezioni che coprono vari aspetti dell’architettura RISC-V:

- Introduzione all’architettura RISC-V: Panoramica sul design pulito e sull’apertura dello standard RISC-V.

- Programma di esempio: Un primo programma in assembly per familiarizzare con la sintassi e l’esecuzione.

- Istruzioni computazionali: Dettagli su istruzioni aritmetiche, logiche, di confronto e di shift.

- Controllo di flusso: Uso di salti, rami e chiamate di funzione.

- Gestione della memoria: Accesso alla memoria, I/O mappato e gestione dello stack.

- Funzioni e convenzioni di chiamata: Uso dei registri, stack e convenzioni per la gestione delle funzioni.

- Architettura privilegiata: Gestione delle eccezioni, livelli di privilegio e registri di controllo.

- Sistema operativo minimale: Introduzione alla scrittura di un sistema operativo di base, inclusi design e codice.

Il segreto è cominciare con programmi di una sola riga, spostando poi l’attenzione sui loop e sui branch. Successivamente, si può passare a scrivere e leggere dalla memoria (array semplici), infine costruire una funzione che calcola qualcosa (es. somma di un array). Si può inserire ogni frammento nell’emulatore e usare il pulsante Step per vedere quali registri cambiano.

Ma non esistono linguaggi ad alto livello per lavorare su RISC-V?

RISC-V non è una nicchia solo per l’assembly: è possibile programmare con linguaggi ad alto livello esattamente come su x86 o ARM. Quel che cambia è solo dove e come il codice è tradotto in istruzioni RISC-V (compilatore/VM) e il “target” a cui ci si rivolge:

- C / C++: sono linguaggi supportati dalla toolchain GNU per RISC-V (

riscv-gnu-toolchain), che permette sia build per Linux (glibc) che toolchain embedded (newlib). In questo secondo caso, il codice è destinato a girare su microcontrollori o sistemi bare-metal, cioè senza sistema operativo. La libreria C newlib è più leggera e minimale: fornisce solo le funzioni base (printf,malloc, ecc.). - LLVM/Clang: anche LLVM ha backend RISC-V maturo, quindi è possibile ricorrere a clang/lld per generare binari RISC-V funzionanti.

- Rust: questo linguaggio, noto per le garanzie intrinseche in termini di sicurezza della memoria, supporta direttamente RISC-V.

- Go: il runtime Go e l’assembler del progetto Go includono supporto per

riscv64; il porting è attivo e in crescita. - Applicazioni ad alto livello (Python, Java, Node.js,…): dove gira Linux su RISC-V (es. distro come Debian/riscv64) si possono eseguire interpreti/VM convenzionali. Quindi Python, OpenJDK, Node.js e simili sono eseguibili su hardware o VM RISC-V.

Scegliendo un linguaggio alto livello su RISC-V si ha il vantaggio di poter contare su uno sviluppo veloce e su meno errori rispetto all’assembly. Rust, come già evidenziato, offre sicurezza della memoria con prestazioni simili al C: è quindi ottimo per kernel o firmware moderni. Inoltre, C/C++ e LLVM/GCC offrono strumenti maturi, mentre Go è comodo per servizi e networking.

Il vantaggio principale di misurarsi con assembly su RISC-V e la forza di progetti come EasyRISC-V non è tanto “fare le cose più velocemente”, quanto comprendere profondamente come funziona la macchina e acquisire competenze che i linguaggi di alto livello nascondono.

/https://www.ilsoftware.it/app/uploads/2025/10/RISC-V-assembly-programmazione.jpg)

/https://www.ilsoftware.it/app/uploads/2026/03/codespeak-sviluppo-software.jpg)

/https://www.ilsoftware.it/app/uploads/2026/03/ESP32-P4-PoE-controller-magnifico.jpg)

/https://www.ilsoftware.it/app/uploads/2026/03/tony-hoare-quicksort-null.jpg)

/https://www.ilsoftware.it/app/uploads/2024/07/github-copilot-copyright-codice-open-source.jpg)