IBM è una delle aziende che investe maggiormente in ricerca, sviluppo e innovazione e ciò appare evidente quando vengono presentati nuovi processori.

Si tratta di dispositivi per le aziende e principalmente destinati al mondo dei data center ma si mettono spesso in evidenza per qualche particolarità e scelta tecnica interessante rispetto agli altri produttori.

L’aspetto curioso del nuovo processore IBM Telum è che esso rinuncia completamente alla cache di livello 3 comune a tutti gli altri processori oggi sul mercato.

In un altro articolo abbiamo visto cos’è la cache di un processore e come funziona.

L’eliminazione della cache L3 è stata determinata dalla volontà di IBM di migliorare le prestazioni anche se ciò, di primo acchito, può sembrare una contraddizione.

Nella cache vengono conservate le informazioni che con buona probabilità verranno utilizzate dai core del processore e che prevedibilmente saranno richieste in un breve lasso di tempo. La cache L3, che viene sfruttata al di sopra di quelle di livello inferiore, ha dimensioni generosa ma anche la più lenta delle tre. Pur essendo implementata in modo diverso sulle piattaforme Intel e AMD la cache L3 è in questo caso comune a tutti i core e contribuisce a ottimizzare significativamente le prestazioni.

Più grande è la cache, però, più elevata è la latenza introdotta: il core deve attingere a un processore che contiene più informazioni e come un volume composto da tante pagine è più complicato da “interrogare” per cercare i dati che servono. Inoltre, il dato conservato in cache è di fatto lontano dal core stesso che dovrà elaborarlo introducendo un’ulteriore latenza.

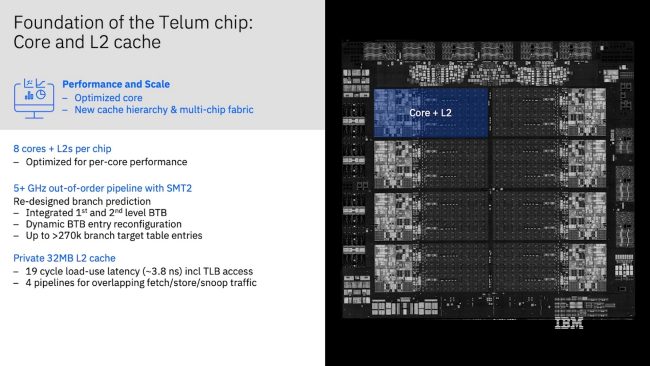

Ciò che gli ingegneri di IBM hanno fatto con Telum consiste nell’utilizzo di otto core a oltre 5 GHz, ciascuno con 32 MB di cache L2 dedicata su un chip prodotto a 7 nm.

Un AMD Ryzen, per confronto, sfrutta 512 KB di cache L2 per core quindi Big Blue si è orientata su dimensioni decisamente più importanti. Ciononostante la latenza ne risulta marginalmente accresciuta tanto che si parla di appena 3,8 ns.

Di fatto un processore IBM Telum ha 256 MB di cache L2 complessivi quando un Ryzen 5800X ha 4 MB di cache L2 e 32 MB di cache L3.

L’ulteriore passo avanti compiuto dai tecnici IBM consiste nell’aver utilizzato una interconnessione bidirezionale ad anello che collega le otto cache L2 a 320 GB/s.

Quando i dati vengono espulsi da una cache possono così essere riposizionati nella cache di qualche altro core come se si trattasse di cache L3 contrassegnandoli con un’apposita etichetta. In ultima analisi quello che IBM ha realizzato è una versatile e veloce “cache L3 virtuale” da ben 256 MB.

Il chip Telum viene incapsulato in un unico pacchetto con un’interconnessione ad alte prestazioni così da inserire fino a 16 core nello stesso processore e poter abilitare l’utilizzo di 512 MB di cache L2.

Telum include anche un acceleratore per le elaborazioni di intelligenza artificiale con una potenza computazionale fino a 6 TeraFLOPS.

Maggiori informazioni su Telum sono condivise da IBM in un video pubblicato su YouTube.

/https://www.ilsoftware.it/app/uploads/2023/05/img_23464.jpg)

/https://www.ilsoftware.it/app/uploads/2025/07/debug-chip-snapdragon-porta-usb-nascosta.jpg)

/https://www.ilsoftware.it/app/uploads/2025/06/fedora-supporto-i686.jpg)

/https://www.ilsoftware.it/app/uploads/2025/06/samsung-gexynos-2500.jpg)

/https://www.ilsoftware.it/app/uploads/2025/06/intel-18a-informazioni-ufficiali.jpg)