/https://www.ilsoftware.it/app/uploads/2023/05/img_21853.jpg)

TSMC è uno dei principali produttori di semiconduttori al mondo: i suoi chip vengono utilizzati da colossi quali Apple, AMD e NVidia oltre che da aziende di più piccole dimensioni. La società taiwanese offre diversi processi produttivi che vanno da 90 a 5 nm: Nanometro, unità di misura utilizzata per descrivere le CPU: ecco perché.

I rappresentanti di TSMC non si fanno scrupoli, anche e soprattutto per finalità di marketing, di condividere le informazioni tecniche sui processi litografici usati dall’azienda mentre non parlano quasi mai pubblicamente di prezzi. Il motivo è evidentemente legato alla volontà di non offrire alcun vantaggio alla concorrenza.

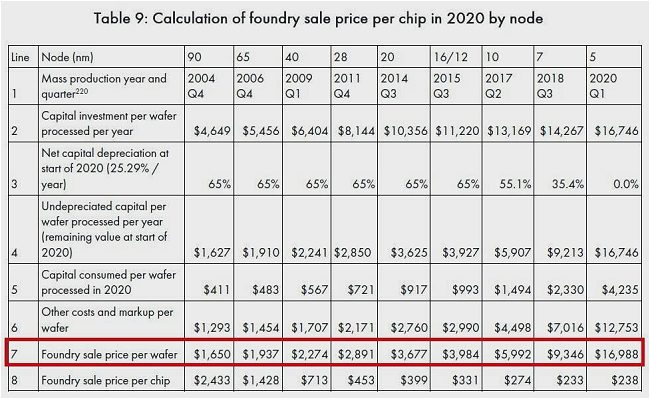

In queste ore è apparsa in rete una tabella che mostra i prezzi che TSMC praticherebbe ai suoi clienti e richiederebbe per le lavorazioni sui vari tipi di wafer in silicio.

Il documento è stato elaborato dal CSET (“Center for Security and Emerging Technology” di Georgetown negli Stati Uniti) e ha come fine ultimo quello di dimostrare, dati alla mano, quanto costa per un’azienda sviluppare e immettere sul mercato un chip di intelligenza artificiale all’avanguardia.

Come si vede nella figura i costi sono davvero impressionanti: per lavorare su un wafer di silicio prodotto a 90 nm, TSMC chiede 1.650 dollari.

Un wafer prodotto con un processo all’avanguardia, ad esempio, a 7 nm costa ben 9.346 dollari. Nel caso del più aggiornato processo litografico a 5 nm chiede ai clienti addirittura 16.988 dollari per il singolo wafer.

Ovviamente la miniaturizzazione sempre più spinta dei processi produttivi aumenta complessità e costi. D’altra parte però, con un solo wafer è possibile ottenere un maggior numero di chip: ne parlavamo nell’articolo Perché i wafer di silicio sono sempre rotondi?.

Non è però tutto “rose e fiori”: estremizzando i processi litografici il numero dei chip difettosi generati a partire dal wafer di silicio tende ad aumentare in maniera significativa. Quindi non è conveniente per il committente puntare su processi che non riescano ad assicurare un yield sufficiente ovvero un numero congruo di chip che superano le ispezioni dal punto di vista funzionale.

Il processo a 5 nm di TSMC è ancora scarsamente utilizzata: è stata Apple la prima a sceglierlo per il suo nuovo balzo in avanti ovvero per la realizzazione del SoC A14.

Decisamente più maturi e affidabili sono invece i predecessori a 7, 10 e 14 nm che garantiscono un basso numero di chip difettosi per singolo wafer.

Per il calcolo dei costi praticati da TSMC, gli studiosi del CSET hanno considerato wafer da 300 mm utilizzati per la realizzazione di chip da 90,7 miliardi di transistor o 610 mm2. Si tratta di un dato che non è stato scelto a caso perché corrisponde con quella dell’acceleratore NVidia Tesla P100 utilizzato principalmente nei data center. Il chip P100, realizzato a 16 nm, consta di 15,3 miliardi di transistor.

Ha poco senso realizzare chip di così grandi dimensioni con un processo litografico particolarmente “spinto”.

Calcolatrice alla mano, prendendo per buone le stime del CSET sull’attività produttiva di TSMC, con un wafer di silicio si potranno produrre 600 chip Apple A14 da 100 mm2 con un costo unitario di 32 dollari ipotizzando un tasso di riuscita dell’85%.

Se si guarda ai chip GA102 di NVidia, “freschi di produzione” con il lancio delle nuove schede grafiche RTX30 (Come funziona il chip Ampère GA102 delle nuove schede NVidia RTX 30), il costo per singolo chip dovrebbe aggirarsi sugli 80 dollari.

Va detto che NVidia ha scelto Samsung come partner per la realizzazione dei suoi chip.

/https://www.ilsoftware.it/app/uploads/2024/12/smart-glasses-scaled-scaled-1-224x120.webp)

/https://www.ilsoftware.it/app/uploads/2025/07/iPhone8Plus_iPhone8_water_inline.jpg.large_2x.jpg)

/https://www.ilsoftware.it/app/uploads/2025/07/gpu-asus-5-kg-oro.jpg)

/https://www.ilsoftware.it/app/uploads/2025/07/wp_drafter_482913.jpg)