Il processo costruttivo a 7 nm di TSMC viene attualmente “spremuto” da AMD che lo sta utilizzando per i suoi prodotti di nuova generazione, CPU e GPU.

La società taiwanese, la più grande fabbrica indipendente di semiconduttori al mondo, ha in questi giorni voluto offrire una serie di interessanti dettagli sul “gradino superiore” ossia il nuovo processo litografico a 5 nm.

Con i nuovi sforzi TSMC intende ampliare ulteriormente il gap rispetto a Samsung e Intel: AMD ne approfitterà in vista dei suoi futuri chip basati su architettura Zen 4?

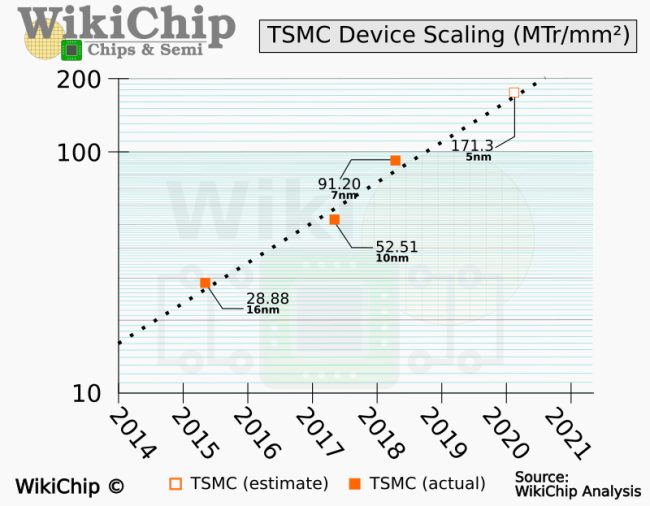

Sono passati appena 5 anni da quando TSMC ha lanciato sul mercato il suo FinFET a 16 nm con una densità di 28,88 milioni di transistor per mm2 e già entro dicembre 2020, stando a quanto riferito, l’azienda produrrà i primi chip a 5 nm.

Sebbene TSMC non abbia ancora fornito dati sulla densità del processo litografico a 5 nm, varie fonti indicano che si potrebbero superare i 171 milioni di transistor per mm2, un valore quasi doppio rispetto a quello che contraddistingue l’attuale processo a 7 nm (91,2 milioni di transistor per mm2).

Quello a 5 nm sarà il primo processo di TSMC interamente gestito ricorrendo alla litografia ultravioletta estrema (EUV): ciò significa lunghezza del gate di ciascun transistor ulteriormente accorciata e “pinne” del FinFET più basse (vedere Processori e memorie: la tecnologia Nanosheet per i transistor renderà FinFET obsoleta).

Secondo gli ingegneri di TSMC i nuovi SoC realizzati a 5 nm, che integrano logica, SRAM e I/O in misura pari, rispettivamente, al 60%/30%/10% dell’intero chip, subiranno una riduzione in termini di dimensioni del 35-40% rispetto agli attuali a 7 nm.

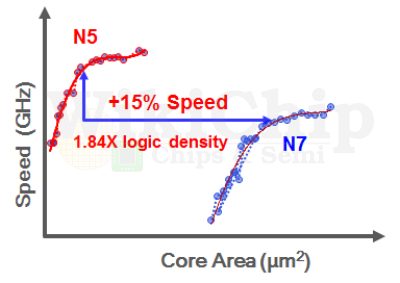

Non solo. Sempre stando a quanto rivelato da TSMC i SoC a 5 nm saranno fino al 15% più prestazionali oppure permetteranno, a parità di performance, un consumo energetico il 30% più basso. Usando nuovi transistor eLVT, inoltre, TSMC promette un balzo in avanti ancora più marcato: fino al 25% a discapito però della densità.

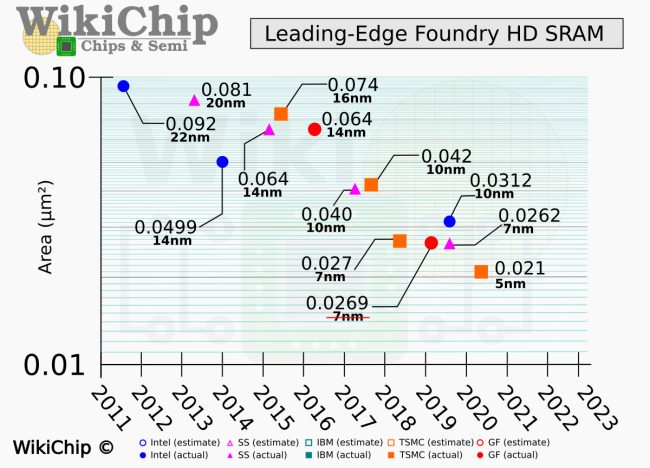

A seconda delle esigenze dei progettisti delle aziende partner, TSMC metterà a disposizione due varianti di SRAM per i futuri SoC: una ad alte prestazioni, l’altra ad alta densità. Per dare qualche numero, la cella ad alte prestazioni misurerà 0,025 µm2 mentre quella ad alta densità al massimo 0,021 µm2. In entrambi i casi, ad oggi, si tratta comunque di “valori record”.

TSMC si appresta insomma a lanciare, nel 2021, un processo litografico che quasi certamente la porrà in condizione di leadership assoluta. Anche se è vero che non è possibile confrontare direttamente i processi costruttivi di ciascun produttore (vedere Nanometro, unità di misura utilizzata per descrivere le CPU: ecco perché), AMD potrebbe di fatto trovarsi in una condizione di vantaggio competitivo rispetto alla rivale Intel per immettere sul mercato i prodotti RDNA 3/Navi 3X.

/https://www.ilsoftware.it/app/uploads/2023/05/img_20968.jpg)

/https://www.ilsoftware.it/app/uploads/2025/07/debug-chip-snapdragon-porta-usb-nascosta.jpg)

/https://www.ilsoftware.it/app/uploads/2025/06/fedora-supporto-i686.jpg)

/https://www.ilsoftware.it/app/uploads/2025/06/samsung-gexynos-2500.jpg)

/https://www.ilsoftware.it/app/uploads/2025/06/intel-18a-informazioni-ufficiali.jpg)