/https://www.ilsoftware.it/app/uploads/2023/06/tecnologia-produzione-chip-TSMC.jpg)

Durante l’European Technology Symposium 2023, il noto produttore taiwanese TSMC ha fornito alcuni interessanti dettagli sul suo nodo di processo a 2 nm.

La miniaturizzazione dei transistor utilizzati all’interno dei chip è un aspetto fondamentale nel campo dei semiconduttori e dell’ingegneria dei microprocessori. È una tendenza che ha guidato l’industria dei semiconduttori per diverse decadi, portando a una costante riduzione delle dimensioni dei transistor, all’aumento delle prestazioni dei chip e anche a consumi energetici più contenuti.

Tuttavia, raggiungere dimensioni di transistor sempre più piccole ci pone dinanzi a sfide significative. Con la miniaturizzazione estrema, i transistor si avvicinano ai limiti fisici delle dimensioni atomiche e possono verificarsi fenomeni quantistici, capaci di influenzare il comportamento del chip. La portata della sfida alla quale siamo giunti richiede nuove tecniche di progettazione e materiali avanzati per mantenere prestazioni affidabili e ridurre la dissipazione di potenza.

Fino ad oggi l’unità di misura migliore per descrivere le dimensioni di un transistor è stata il nanometro. Con il nodo di processo a 2 nm, come quello presentato da TSMC, siamo veramente arrivati a sfiorare il limiti fisici. D’altra parte, Intel ha aperto all’era angstrom: 20Å (angstrom) equivalgono appunto a 2 nm. Inoltre, Intel e ARM hanno stipulato un accordo per creare SoC a 18Å negli anni a venire.

Cos’è un nodo di produzione e cosa sono TSMC N2 e N2P

Nel contesto della realizzazione dei chip, il termine “nodo di produzione” si riferisce alla tecnologia di processo utilizzata per fabbricare i chip stessi. È un indicatore delle prestazioni e dell’efficienza dei chip. Solitamente, come abbiamo osservato in precedenza, un nodo più piccolo corrisponde a una maggiore densità di transistor, prestazioni migliorate e una maggiore efficienza energetica. Le dimensioni più ridotte consentono di posizionare più transistor all’interno dello stesso spazio fisico, aumentando la complessità e le prestazioni dei chip.

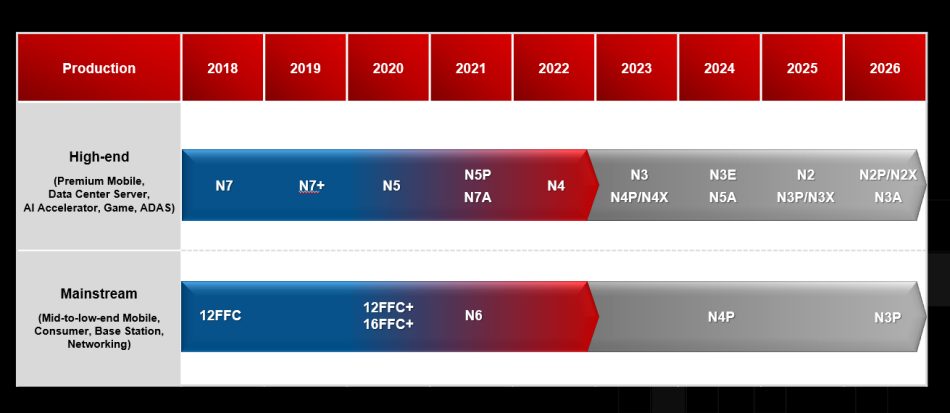

I portavoce di TSMC hanno spiegato che l’azienda è impegnata sui nodi di processo N2 e N2P. Entrambi sono stati sviluppati tenendo conto delle esigenze del calcolo ad alte prestazioni (HPC), quindi presentano una serie di miglioramenti progettati specificamente per migliorare le performance. Tuttavia, anche le applicazioni a basso consumo trarranno vantaggio dai nuovi nodi TSMC in quanto le prestazioni per watt rispetto ai predecessori risulteranno a loro volta superiori.

TSMC adotta lo schema GAAFET per i transistor

Il nodo di produzione N2, primo a utilizzare lo schema GAAFET, promette di aumentare le prestazioni dei transistor del 10-15% a parità di potenza e complessità o di ridurre il consumo energetico del 25-30% mantenendo inalterati numero di transistor e velocità di clock.

Con la tecnologia GAAFET (Gate-All-Around Field-Effect Transistor), TSMC abbraccia l’evoluzione dei transistor FinFET. Mentre questi ultimi hanno un canale di conduzione tridimensionale con una “pinna” circondata dal gate, i transistor GAAFET presentano un canale di conduzione completamente circondato dal gate.

Tra i principali vantaggi di GAAFET, un migliore controllo del canale di conduzione (maggiore controllo sulla corrente che fluisce attraverso il dispositivo), una maggiore densità di transistor, la riduzione delle perdite di potenza, un migliore controllo delle tensioni di soglia (tensioni richieste per attivare e spegnere il transistor), la possibilità di realizzare transistor ancora più ridotti.

L’erogazione di potenza è una delle pietre miliari quando si tratta di migliorare le prestazioni dei transistor e i processi di produzione. I nodi N2 e N2P introducono diverse innovazioni relative alle interconnessioni per ottimizzare ulteriormente le prestazioni aggiuntive. Con N2P, inoltre, TSMC introduce il power rail (infrastruttura elettrica che fornisce l’alimentazione ai componenti e ai blocchi funzionali presenti all’interno del chip) sul dorso per ottimizzare l’erogazione di potenza e l’area del die.

N2 dovrebbe debuttare nella seconda metà o nella parte finale del 2025; N2P, invece, è atteso per il 2026-2027.

Le immagini utilizzate nell’articolo sono di TSMC.

/https://www.ilsoftware.it/app/uploads/2026/04/chip-intel-serpent-lake-nvidia-rtx.jpg)

/https://www.ilsoftware.it/app/uploads/2026/04/collaborazione-intel-arm.jpg)

/https://www.ilsoftware.it/app/uploads/2026/03/intel-core-ultra-series-3-processori-business.jpg)

/https://www.ilsoftware.it/app/uploads/2026/03/chip-arm-agi-cpu.jpg)