Intel ha compiuto un passo senza precedenti nell’industria dei semiconduttori installando e testando con successo ASML Twinscan EXE:5200B, il primo scanner High-NA EUV al mondo pensato per la produzione commerciale di chip avanzati. Il traguardo segna la prima volta che una tecnologia di litografia con Numerical Aperture (NA) elevata e luce Extreme Ultraviolet (EUV) viene portata da esperimenti di laboratorio a un contesto produttivo su larga scala, aprendo la strada a processi con dimensioni dei transistor fino a una manciata di angstrom.

High-NA EUV: cosa significa e perché conta

EUV (Extreme Ultraviolet) è una tecnologia di litografia che utilizza luce ultravioletta con lunghezza d’onda di circa 13,5 nanometri. La litografia è il processo con cui si “stampano” i circuiti dei chip sui wafer di silicio, definendo le forme dei transistor e dei collegamenti tra di essi.

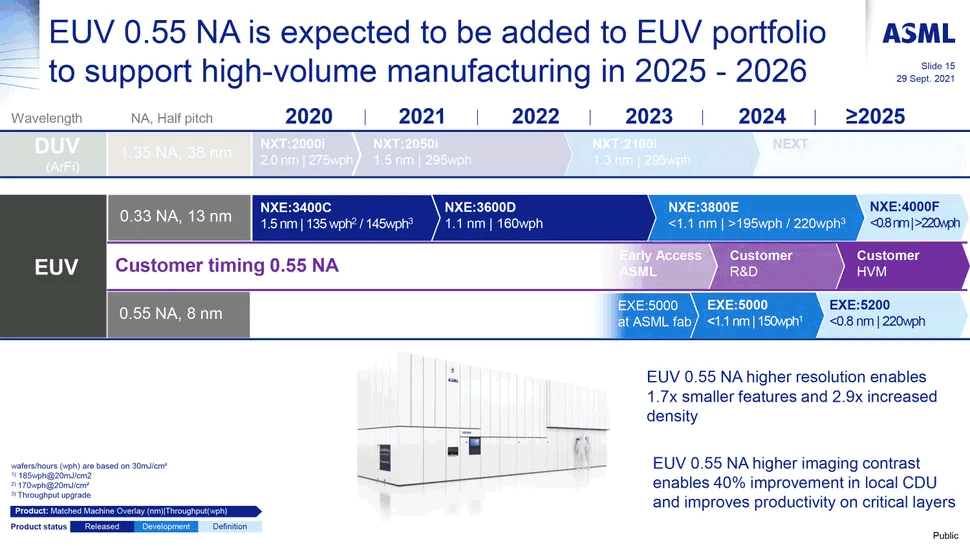

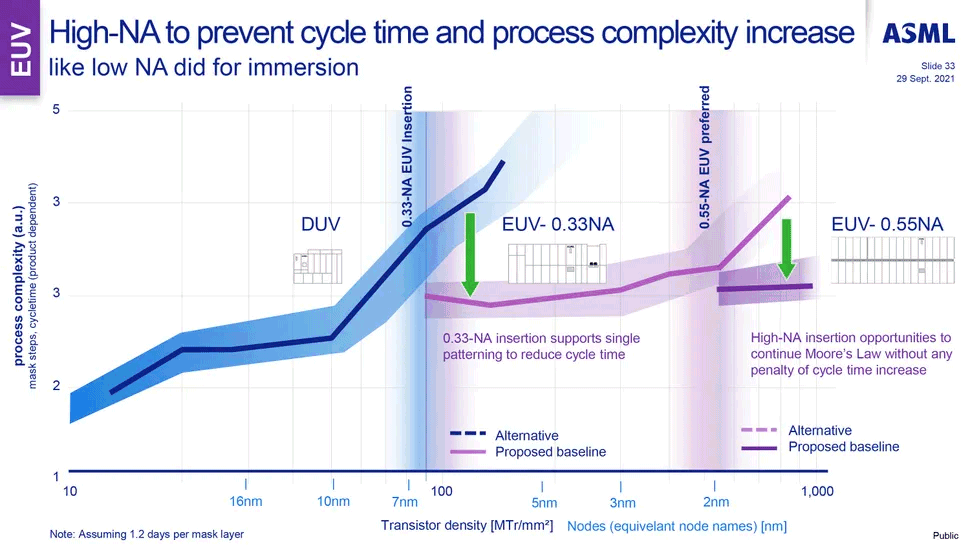

NA (Numerical Aperture) indica la capacità dell’ottica del proiettore di concentrare la luce in dettagli più piccoli: più alto è il valore, più piccoli e precisi possono essere i circuiti. La EXE:5200B ha un NA di 0,55, mentre gli strumenti Low-NA tradizionali si fermano a 0,33 circa. Questo significa che EXE:5200B può “stampare” dettagli di circa 8 nanometri, rispetto ai 13 nanometri dei sistemi precedenti, senza dover ricorrere a processi complicati chiamati multi-patterning (più passaggi di esposizione per ottenere dettagli più fini).

Overlay: l’allineamento dei layer

Nei chip moderni, i circuiti non sono monostrato, ma si costruiscono a più livelli sovrapposti. L’overlay misura quanto uno strato è allineato rispetto a quello sottostante. EXE:5200B raggiunge un overlay di 0,7 nm, un valore incredibilmente preciso: per capire l’ordine di grandezza, è meno di un decimo della larghezza di un virus. Una caratteristica essenziale perché anche piccoli errori possono ridurre le rese (yield), cioè la percentuale di chip funzionanti per wafer prodotto.

EXE:5200B può processare fino a 175 wafer all’ora. I wafer sono dischi di silicio su cui vengono fabbricati i chip. La gestione di questi wafer è affidata a un sistema chiamato wafer stocker, che li conserva e li espone correttamente. Intel e ASML hanno riprogettato lo stocker per ridurre il fenomeno del drift termico e meccanico, cioè le variazioni di temperatura e posizionamento che possono compromettere la precisione; per migliorare la stabilità produttiva, riducendo la necessità di ricalibrazione frequente; per rendere più fluido il flusso dei lotti in produzione.

Intel 14A: cosa significa e perché è importante

La società di Santa Clara utilizzerà EXE:5200B per sviluppare il nodo costruttivo 14A, il prossimo che rappresenterà un punto di svolta tecnologico e strategico nell’industria dei semiconduttori.

Con il nome Intel 14A (14 angstrom) si fa riferimento al nome commerciale del prossimo nodo logico di Intel, in cui l’unità di misura “angstrom” (1 Å = 0,1 nm) indica la scala delle dimensioni dei transistor. In pratica, i transistor 14A avranno caratteristiche di dimensione nell’ordine di 1,4 nm per i layer più avanzati, pur restando compatibili con una produzione industriale ad alto volume.

Sappiamo che Intel potrebbe tornare a produrre chip per Apple e che l’azienda sta sgomitando per riacquistare velocemente il favore di altri produttori fabless (sprovvisti quindi di stabilimenti propri). Riuscire a lanciare senza problemi un processo come Intel 14A porterebbe vantaggi cruciali per l’azienda guidata da Lip-Bu Tan:

- Scalabilità dei transistor: permette di inserire più transistor nello stesso chip, aumentando le prestazioni e riducendo i consumi per watt.

- Abilitazione dell’High-NA EUV: il 14A sarà il primo nodo a sfruttare High-NA EUV per i layer critici, eliminando in gran parte la necessità di multi-patterning e migliorando rese e tempi di ciclo.

In termini pratici, il 14A consente a Intel di definire linee e spaziature più sottili rispetto ai nodi precedenti; aumentare flessibilità progettuale per i designer di chip; ridurre numero di maschere e passaggi di esposizione, quindi abbattere complessità e costi; massimizzare la produttività dei wafer e le rese dei chip finiti.

Il futuro oltre il silicio: transistor 2D

Intel non si ferma qui. A lungo termine, i transistor in silicio rischiano di raggiungere i loro limiti fisici: troppo sottili, con perdita di controllo elettrostatico e mobilità dei portatori di carica ridotta. La soluzione possibile sono i materiali 2D, strati atomici che possono fungere da canali dei transistor senza i problemi dello spessore ridotto del silicio.

Intel e Imec hanno dimostrato per la prima volta che i 2DFET (transistor a effetto campo su materiali 2D) possono essere integrati su wafer standard da 300 mm, con processi compatibili con la produzione industriale. L’innovazione chiave è il damascene top contact, un metodo che permette di realizzare contatti elettrici stabili senza danneggiare i fragili strati 2D.

Perché questa doppia scommessa è essenziale per Intel

Grazie ai recenti avanzamenti nei suoi stabilimenti produttivi, Intel dimostra di saper combinare innovazione tecnologica e “manifatturabilità industriale“, non soltanto tenendo per sé ma anche garantendo ai clienti soluzioni affidabili per scenari futuri estremamente complessi.

High-NA EUV risolve problemi di miniaturizzazione e produttività nel breve-medio termine; 2DFET prepara il terreno per i transistor post-silicio, possibili dal 2030 in poi.

/https://www.ilsoftware.it/app/uploads/2025/12/produzione-chip-intel-14A.jpg)

/https://www.ilsoftware.it/app/uploads/2026/03/APU-AMD-nuova-generazione-medusa-point.jpg)

/https://www.ilsoftware.it/app/uploads/2026/03/CPU-Intel-Core-Ultra-270K-Plus-250K-Plus.jpg)

/https://www.ilsoftware.it/app/uploads/2026/03/windows-11-ottimizzazioni-AMD-Zen-6.jpg)

/https://www.ilsoftware.it/app/uploads/2026/03/xeon-6-plus-intel.jpg)