A marzo scorso ARM ha aggiornato la sua architettura big.LITTLE lanciando DynamIQ: ARM presenta la tecnologia DinamIQ, evoluzione di big.LITTLE.

Mentre la prima consente la realizzazione di processori basati su più cluster eterogenei all’interno dei quali vengono usati core dello stesso tipo, DynamIQ consente l’utilizzo di cluster eterogenei composti da core di diversa tipologia.

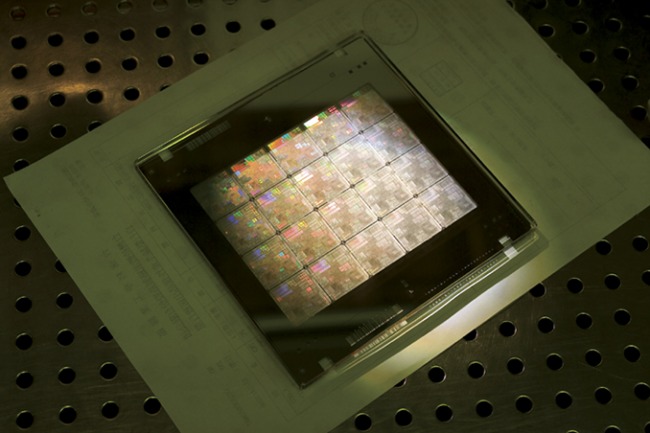

Adesso TSMC, Xilinx, ARM e Cadence hanno annunciato che inizieranno a provare i primi chip DynamIQ realizzati ricorrendo a un processo costruttivo FinFET a 7 nm entro marzo 2018.

L’obiettivo è, per il momento, quello di creare chip da destinarsi ai data center per dimostrare quanto la piattaforma ARM possa essere ormai usata in ambito server o comunque asservire alle più complesse (ed esigenti in termini di risorse computazionali) applicazioni per l’intelligenza artificiale.

Xilinx, che dispone di una notevole esperienza nel campo, userà un bus CCIX (Cache Coherent Interconnect for Accelerators) per collegare i chip DynamIQ (probabilmente saranno usati Cortex A55 e A75) con i suoi FPGA (Field Programmable Gate Array), soluzione alla quale stanno guardando molti “big” dell’industria per sviluppare hardware specializzato per il machine learning: Microsoft Brainwave, intelligenza artificiale su chip FPGA.

Gli acceleratori FPGA sono infatti chip riprogrammabili via software, scalabili, molto semplici e più efficienti rispetto a una CPU di tipo tradizionale.

Un approccio come quello a cui si sta guardando promette una maggiore ampiezza di banda e latenze nettamente più contenute, grazie anche al bus CCIX.

Cadence, da parte sua, fornirà i controller che si occuperanno di gestire l’accesso alla memoria DDR4 e alle piste PCIe 3.0 e PCIe 4.0.

/https://www.ilsoftware.it/app/uploads/2023/05/img_16122.jpg)

/https://www.ilsoftware.it/app/uploads/2024/01/2-97.jpg)

/https://www.ilsoftware.it/app/uploads/2023/10/versione-BIOS-UEFI-windows.jpg)

/https://www.ilsoftware.it/app/uploads/2024/09/1-1.jpg)

/https://www.ilsoftware.it/app/uploads/2025/02/2.png)