Il MIT (Massachusetts Institute of Technology) è una fucina di nuove idee e tecnologie innovative. Per questo motivo la famosissima università di ricerca statunitense detiene una miriade di brevetti. Molti di essi hanno a che fare con il grafene, materiale dalle caratteristiche uniche (tra le tante, vanta la resistenza meccanica del diamante e la flessibilità della plastica) che al momento non si è ancora riusciti a impiegare con un effettivo abbattimento dei costi di produzione (vedere anche Grafene, materiale super-resistente ora anche 3D).

Il MIT ha appena presentato un prototipo di chip che poggia il suo funzionamento su una nuova architettura, dotata dei suoi propri circuiti di elaborazione e storage.

L’obiettivo dei ricercatori è superare in toto tutte quelle limitazioni che attualmente insistono sul trasferimento dei dati tra memoria, processore e memorie di massa nel caso della storica e universalmente adottata architettura x86.

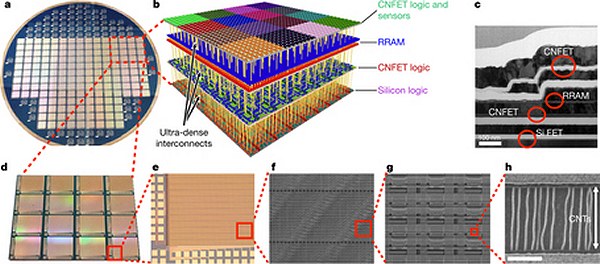

Il chip descritto dagli esperti del MIT si sviluppa su più livelli: gli attuali processi litografici non consentono l’utilizzo di una simile struttura perché i transistor vengono fissati a temperature oltre i 1.000 °C. Se si provassero a “impilare” più livelli di transistor, quelli sottostanti ne risulterebbero inevitabilmente danneggiati.

Utilizzando nanotubi di carbonio per la realizzazione di ciascun livello non v’è invece alcun problema nella sovrapposizione perché le temperature in gioco sono, questa volta, dell’ordine dei 200 °C.

Il campione mostrato da MIT impiega un substrato sul quale risiede parte della logica; sopra di esso è posizionato un livello CNFET (transistor a effetto di campo basato su nanotubi di carbonio); ancora più in alto un livello che ospita memoria non volatile RRAM (Resistive Random Access Memory) e infine un altro CNFET con sensori integrati.

L’approccio proposto dagli studiosi del MIT permette un utilizzo ragionato dello spazio disponibile e apre le porte, in futuro, all’utilizzo di chip integrati anche sui sistemi desktop, notebook e server. Chip che saranno ultra-performanti grazie all’eliminazione di tutti i colli di bottiglia tra processore, storage e memoria.

Per realizzare il suo prototipo, il MIT ha usato un milione di celle RRAM e due milioni di celle CNFET configurando il chip appena presentato come la nanostruttura più complessa mai creata fino ad oggi.

Come ogni altro prodotto basato sull’impiego del grafene non è dato sapere quando un chip del genere sarà commercialmente disponibile.

/https://www.ilsoftware.it/app/uploads/2023/05/img_15775.jpg)

/https://www.ilsoftware.it/app/uploads/2024/04/chip-amd-ryzen-ai-pro-8000.jpg)

/https://www.ilsoftware.it/app/uploads/2024/04/google-axion-cpu-ARM.jpg)

/https://www.ilsoftware.it/app/uploads/2024/04/acceleratore-intel-gaudi-IA.jpg)

/https://www.ilsoftware.it/app/uploads/2024/04/microcodice-AMD-architettura-AM5-plus.jpg)