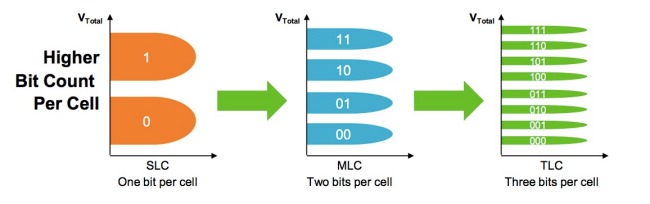

Le memorie NAND utilizzate nelle unità SSD differiscono sulla base del numero di bit che possono essere conservati: SLC (single level cell, un bit); MLC (multi-level cell, due bit); TLC (triple-level cell, tre bit); QLC (quad-level cell, quattro bit).

Ogni cella può quindi conservare al suo interno due, quattro, otto o sedici possibili valori (21, 22, 23 o 24) esprimibili con diversi livelli di tensione.

I valori di tensione possono essere approssimati: nelle memorie SLC il valore 0 si esprime ponendo la tensione nella “finestra” compresa tra 0 e 5 V; il valore 1 è rappresentato con un livello di tensione compreso tra 6 e 11 V.

Utilizzando memorie capaci di immagazzinare un numero maggiore di bit, le “finestre” si riducono notevolmente dal momento che aumentano i valori da gestire.

Con il trascorrere del tempo, specie nel caso delle unità SSD TLC e QLC, potrebbe non essere semplice recuperare o scrivere con accuratezza i valori corretti agendo sulle tensioni. Vari studi hanno infatti confermato che il nemico più temibile per la corretta conservazione dei dati e, quindi, per la loro integrità è il tempo e non il numero di scritture effettuate sull’unità SSD.

Nell’articolo SSD QLC, sono veloci e affidabili anche se sulla carta non dovrebbero esserlo abbiamo rimarcato che anche le recenti unità SSD QLC, diversamente rispetto a quanto si potrebbe pensare, si rivelano affidabili.

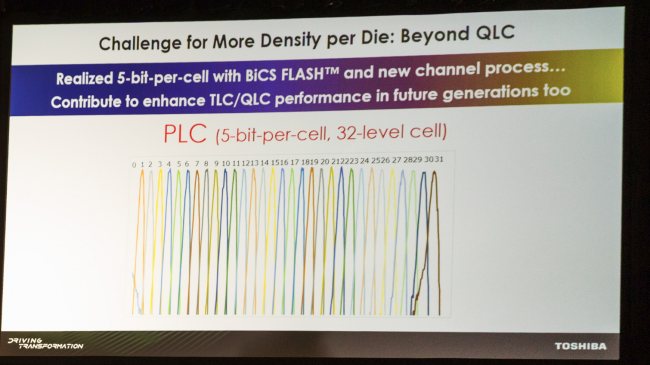

Toshiba ha fatto presente di essere al lavoro sullo sviluppo delle memorie che in futuro potrebbero raccogliere l’eredità delle QLC.

Si chiameranno NAND PLC (penta-level cell) e consentiranno di memorizzare cinque bit per cella ovvero ben 32 valori esprimibili utilizzando altrettanti livelli di tensione.

Le memorie PLC consentiranno ovviamente di aumentare ancora la densità pur esacerbando le problematiche con le quali i produttori hanno dovuto fino ad oggi fare i conti.

Nell’immagine si possono vedere i valori che Toshiba conserverà nelle sue nuove memorie PLC, nell’intervallo compreso tra 0 e 11 V con un margine di circa 300 mV per ogni possibile valore.

I requisiti ai quali fa riferimento Toshiba implicheranno una maggiore precisione nel salvataggio e nella lettura delle tensioni. I tecnici dell’azienda hanno comunque raccolto la sfida sostenendo di essere già a buon punto grazie a una serie di modifiche applicate sulle attuali memorie QLC.

Toshiba spiega che alcune nuove caratteristiche del protocollo NVMe come Zoned Namespaces (ZNS) aiuteranno a mitigare alcune delle problematiche. ZNS, per esempio, aiuterà a ridurre la cosiddetta write amplification (vedere SSD, come funzionano le tecnologie che li rendono più veloci), la necessità di ricorrere all’over provisioning e l’utilizzo della DRAM interna migliorando throughput e latenza.

/https://www.ilsoftware.it/app/uploads/2023/05/img_19805.jpg)

/https://www.ilsoftware.it/app/uploads/2025/02/novita-SSD-samsung-9100-PRO.jpg)

/https://www.ilsoftware.it/app/uploads/2025/07/myqnapcloud-one-presentazione.jpg)

/https://www.ilsoftware.it/app/uploads/2025/06/Edge-AI-Storage-Server.jpg)

/https://www.ilsoftware.it/app/uploads/2025/05/xMEMS-raffreddameno-stato-solido-SSD.jpg)