I principali produttori hardware si accingono a rilasciare la prima “ondata” di dispositivi basati sui nuovi processori Meteor Lake. Nel frattempo, però, Intel sta già guardando alla prossima generazione, conosciuta con il nome in codice di Arrow Lake. L’obiettivo è migliorare le prestazioni in modo significativo. E questa volta l’azienda guidata da Pat Gelsinger gioca una carta un po’ diversa dal solito presentando Intel PowerVia.

Per ottimizzare le performance dei futuri processori, gli ingegneri Intel hanno lavorato sulle modalità di alimentazione. Attualmente, i chip prodotti da Intel e da altri produttori sono realizzati con uno strato superiore di transistor insieme alle interconnessioni di alimentazione. Man mano che i chip diventano più piccoli e densi, gli strati che condividono le interconnessioni di alimentazione sono diventati una rete sempre più complessa che pone un freno alle prestazioni complessive. C’è inoltre il problema dei limiti fisici, figlio della tendenza ad estremizzare il concetto di miniaturizzazione dei chip.

Intel PowerVia: cos’è e come funziona

La nuova tecnologia PowerVia, appena presentata da Intel, ha già portato a significativi progressi sul piano delle prestazioni dei microprocessori. I portavoce dell’azienda affermano inoltre che PowerVia rappresenta anche un modo completamente nuovo di produrre CPU.

La soluzione messa a punto da Intel separa i transistor dalle connessioni di alimentazione sulla parte superiore del chip. I transistor vengono realizzati per primi, con gli strati di interconnessione aggiunti successivamente, sulla parte posteriore del chip.

Disaccoppiando i due processi, i chip possono aumentare prestazioni ed efficienza energetica fornendo risultati migliori. Da decenni le linee di alimentazione e di segnale all’interno dell’architettura dei chip utilizzano le stesse risorse a scapito uno dell’altra. PowerVia interviene proprio in questi termini risolvendo il problema dei colli di bottiglia nelle interconnessioni.

L’alimentazione dalla parte posteriore del chip è di vitale importanza per ridurre le dimensioni dei transistor, consentendo ai progettisti di aumentare la densità senza sacrificare risorse per fornire più potenza e prestazioni.

D’altra parte, un numero sempre crescente di casi d’uso, tra cui l’intelligenza artificiale e la grafica avanzata, richiedono chip basati su transistor più piccoli, più densi e più potenti per soddisfare le esigenze di calcolo.

La tecnologia PowerVia sarà utilizzata nei processori Arrow Lake

PowerVia è in arrivo nei chip Arrow Lake a 20Å (angstrom), equivalenti a 2 nm. Un nodo di produzione che sarà utilizzato negli stabilimenti Intel a partire dalla prima metà del 2024. Abbiamo chiarito il significato in un altro articolo incentrato sui chip a 2 nm.

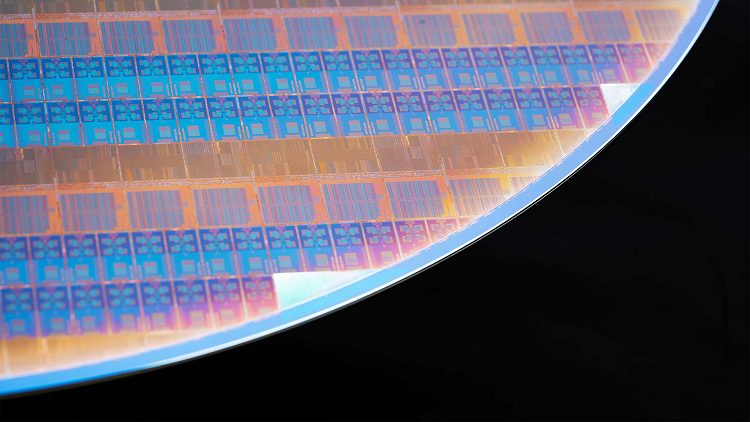

Per adesso, i tecnici Intel hanno provato con successo PowerVia in un chip di prova Blue Sky Creek Meteor Lake (nell’immagine sotto, fonte: Intel). Secondo Ben Sell, Intel Vice President of Technology Development, già in questa fase è stato possibile registrare un aumento della frequenza operativa intorno al 6%. Inoltre, PowerVia offre un utilizzo altamente efficiente delle risorse del chip, più del 90% delle celle nel caso dei core-E. Tanto da far sostenere a Intel che la concorrenza sarebbe un paio di anni indietro nello sviluppo di una soluzione simile.

L’accoppiata PowerVia-EUV per i nuovi processori

Intel afferma che la “litografia EUV (Extreme Ultraviolet) ha consentito un utilizzo delle celle standard superiore al 90% su ampie aree del die“. La litografia EUV è una tecnologia avanzata di fabbricazione di semiconduttori che utilizza luce ultravioletta estrema per creare i pattern necessari sui wafer di silicio. Questa tecnologia consente di ottenere linee più sottili e dettagli più precisi rispetto alle tecniche di litografia tradizionali, consentendo una maggiore densità di transistor sul chip.

Quando si parla di “utilizzo delle celle standard“, ci si riferisce alla disposizione delle unità funzionali all’interno del die (singola unità di un chip di silicio che viene fabbricata sulla superficie di un wafer). Le celle standard sono componenti predefinite utilizzate per costruire circuiti digitali complessi, come porte logiche, flip-flop e memorie.

Con l’utilizzo della litografia EUV, combinato con l’introduzione di PowerVia, Intel sostiene di poter sfruttare le celle standard in modo efficiente, consentendo di posizionarle e interconnetterle in modo più denso e preciso. L’affermazione che l’utilizzo delle celle standard sia superiore al 90% su ampie aree del die indica che il produttore è riuscito a massimizzare l’utilizzo dello spazio sul chip, riducendo al minimo le aree inutilizzate o non funzionali.

Le immagini che raffigurano il wafer di test utilizzato per provare PowerVia sono di Intel.

/https://www.ilsoftware.it/app/uploads/2023/06/intel-powervia-wafer.jpg)

/https://www.ilsoftware.it/app/uploads/2026/04/chip-intel-serpent-lake-nvidia-rtx.jpg)

/https://www.ilsoftware.it/app/uploads/2026/04/collaborazione-intel-arm.jpg)

/https://www.ilsoftware.it/app/uploads/2026/03/intel-core-ultra-series-3-processori-business.jpg)

/https://www.ilsoftware.it/app/uploads/2026/03/chip-arm-agi-cpu.jpg)