/https://www.ilsoftware.it/app/uploads/2023/05/img_19446.jpg)

I primi processori a introdurre il supporto per le specifiche PCIe 4.0 sono gli AMD Ryzen 3000 presentati quest’estate dalla società di Sunnyvale e già i produttori si stanno muovendo per iniziare a valutare l’implementazione di PCIe 5.0, recentemente divenuto standard: Approvato lo standard PCIe 5.0: trasferisce 32 Gbps per singolo canale.

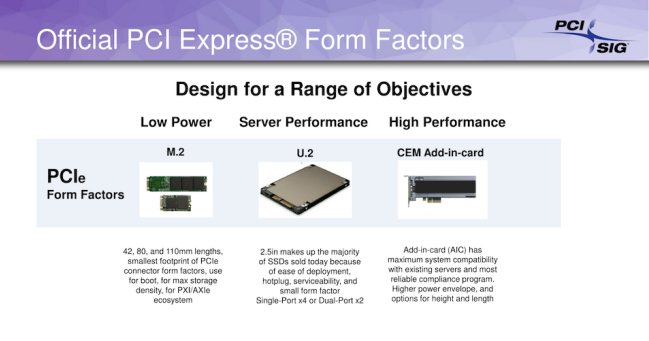

Per la maggior parte degli utenti, però, l’interfaccia PCIe 3.0 continua a rimanere ad oggi un punto di riferimento, anche per ciò che riguarda lo storage, come abbiamo visto nel nostro articolo SSD M2, cosa sono e come scegliere quelli migliori.

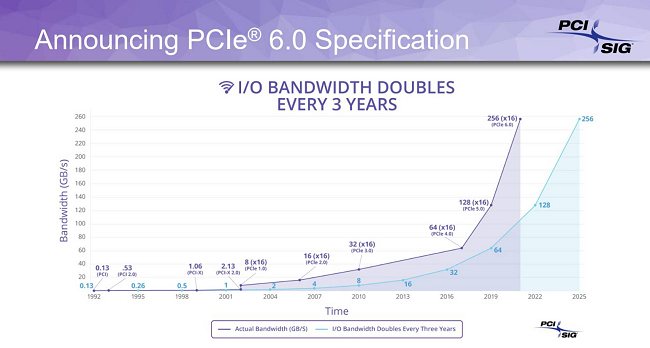

Il PCI-SIG (Peripheral Component Interconnect Special Interest Group), consorzio di aziende operanti nel campo dell’elettronica che si occupa, tra gli altri, dello sviluppo dello standard PCIe (PCI Express), nel frattempo ha confermato di essere già proiettato in ottica futura rilasciando la versione 0.3 delle specifiche PCIe 6.0.

PCIe 6.0 raddoppierà ancora l’ampiezza di banda sul singolo canale portandola a 16 GB/s quadruplicando quindi le prestazioni di PCIe 4.0 e migliorando di otto volte le prestazioni PCIe 3.0 (1 GB/s per singola pista). L’interfaccia ha debuttato a luglio 2019 con il chipset X570 e i processori AMD Ryzen 3000: I nuovi processori Ryzen 3000 funzioneranno meglio con Windows 10 Aggiornamento di maggio 2019.

I dispositivi connessi all’interfaccia PCIe 6.0 potranno usare fino a sedici canali (PCIe x16) per un totale di 256 GB/s di banda.

La veloce maturazione che hanno evidenziato le specifiche PCIe 6.0 ha in parte a che vedere con l’intenzione di Intel di utilizzare l’interfaccia insieme con il suo protocollo CXL (Compute Express Link) del quale abbiamo parlato nell’articolo CXL è la risposta a NVLink: cos’è e che cosa collega.

Le nuove specifiche, che quindi abbracceranno l’utilizzo dell’interfaccia di interconnessione CXL, non saranno comunque pronte prima del 2021. Anche perché qui dovrà essere svolto un imponente lavoro sulla stabilizzazione dei segnali: incrementando le frequenze trasmissive è più difficile assicurarsi che ciascun bit trasferito in una brevissima finestra temporale sia poi adeguatamente ricevuto e ricostruito.

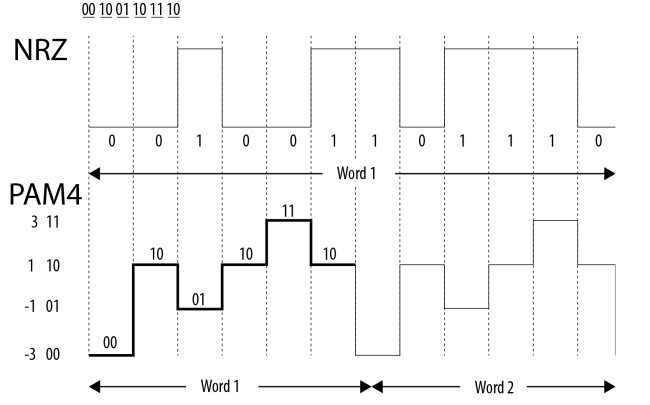

Nel caso di PCIe 6.0, il PCI-SIG ha previsto il passaggio al nuova sistema di trasferimento dei segnali PAM4 che permetterà, attraverso l’utilizzo di opportuni livelli di tensione, di rappresentare non soltanto 0 e 1 ma, complessivamente, quattro stati ovvero 00, 01, 10 e 11.

Il nuovo approccio ha anche il vantaggio di ridurre il rumore introdotto durante le trasmissioni dati anche se, di converso, i consumi energetici tenderanno a salire.

Un ulteriore rovescio della medaglia consiste nella maggiore probabilità di interpretare in modo scorretto i vari livelli di tensione. Per questo motivo PCI-SIG ha in programma l’integrazione di un solido sistema per la correzione dell’errore (Forward error correction o FEC).

La richiesta di una maggiore velocità di comunicazione tra i dispositivi all’interno di un server o tra macchine installate in un data center sta accelerando: lo sviluppo di PCIe insieme a protocolli logici come CXL porterà quindi a una veloce adozione delle specifiche PCIe 5.0 e 6.0, molto di più rispetto a quanto non sta accadendo ancora con PCIe 4.0.

/https://www.ilsoftware.it/app/uploads/2026/05/qualita-driver-windows-11-batteria-prestazioni.jpg)

/https://www.ilsoftware.it/app/uploads/2025/04/ARM-chip-cpu-data-center.jpg)

/https://www.ilsoftware.it/app/uploads/2025/09/meta-ray-ban-display-smart-glass.jpg)

/https://www.ilsoftware.it/app/uploads/2024/02/etichetta-olografica-processori-intel.jpg)