Samsung e TSMC si stanno sfidando per stabilire nuovi record e dimostrare quale delle due società è in grado di far evolvere più rapidamente oltre che in maniera più efficace e convincente il suo processo litografico per la realizzazione dei chip di nuova generazione.

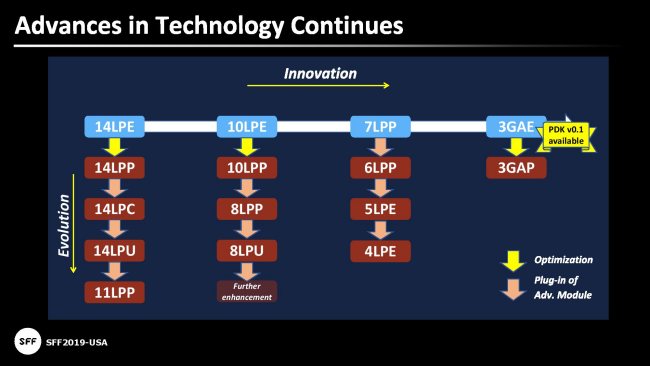

L’azienda sudcoreana sta facendo fruttare i miliardi di dollari spesi annualmente in ricerca e sviluppo ed è proprio per questo motivo che i suoi tecnici hanno iniziato a parlare di processo costruttivo a 3 nm: vedere Nanometro, unità di misura utilizzata per descrivere le CPU: ecco perché.

Alcuni partner di Samsung avrebbero già ottenuto i primi prototipi di chip a 3 nm: si tratta di versioni “alpha” grazie alle quali è comunque possibile iniziare a valutare il design dei futuri SoC.

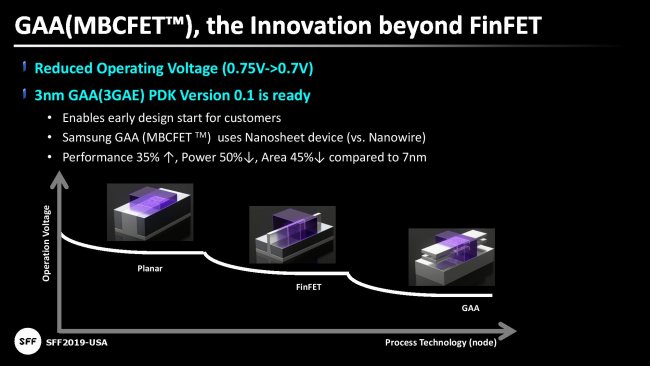

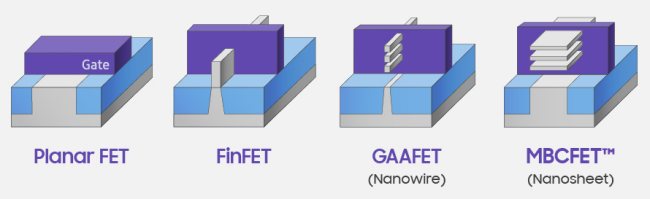

La modifica più importante che segnerà il passaggio ai 3 nm è senza dubbio l’abbandono della tecnologia FinFET, transistor a doppia porta non planare su un substrato SOI (Silicon On Insulator ovvero “silicio su isolante”), per abbracciare i transistor di tipo GAAFET (Gate-all-around FET).

I FinFET sono transistor tri-gate: il canale che mette in comunicazione source e drain (i componenti fondamentali di un transistore MOSFET insieme con il gate) viene portato al di sopra del piano del silicio formando una pinna (“fin” in inglese) che porta numerosi vantaggi rispetto ai tradizionali schemi costruttivi.

Nei GAAFET vengono utilizzati dei “nanocollegamenti” tra source e drain; inoltre il transistor viene dimensionato in maniera tale che il gate sia posizionato al di sotto del canale, non soltanto nelle parti superiore e laterali. Il fine ultimo è quello di impilare i transistor verticalmente anziché muoversi solamente di lato.

Nell’immagine i vari schemi utilizzabili: MBCFET, acronimo di Multi-Bridge Channel FET, è destinato a divenire un marchio registrato di Samsung e descrive un transistor che usa un canale disposto come un foglio orizzontale incrementando il suo volume. Rispetto a un GAAFET “tradizionale”, Samsung ritiene di poter realizzare transistor iper-miniaturizzati con un approccio meno costoso pur conservando benefici in termini di performance e scaling.

Secondo la società asiatica con i transistor FinFET è possibile spingersi al massimo fino a 4 nm mentre per migrare ai 3 nm sarà essenziale passare all’architettura GAAFET/MBCFET. E ciò, a meno di imprevisti, dovrebbe avvenire già nel 2021 con la produzione di massa (schema 3GAE).

La prima versione dei chip MBCFET a 3 nm, inoltre, dovrebbe garantire il 35% di performance in più rispetto al processo costruttivo a 7 nm, ridurre i consumi del 50% e le dimensioni di un 35% circa.

/https://www.ilsoftware.it/app/uploads/2023/05/img_19238.jpg)

/https://www.ilsoftware.it/app/uploads/2025/07/wp_drafter_482869.jpg)

/https://www.ilsoftware.it/app/uploads/2025/03/comandi-rapidi-android.jpg)

/https://www.ilsoftware.it/app/uploads/2025/07/wp_drafter_482839.jpg)

/https://www.ilsoftware.it/app/uploads/2025/03/24.jpg)